RS триггер

Содержание

Триггер в переводе с английского – защёлка. Это электронный модуль, способный длительно находиться в одном устойчивом состоянии и менять его под действием внешнего сигнала. Это цифровая автоматическая ячейка, которая умеет запоминать и хранить двоичный код данных, размером в 1 бит. То, как работает триггер, зависит от его структуры и назначения. В основе всякой подобной ячейки располагается восстанавливающее кольцо из пары инверторов. Устройство содержит прямой и инверсный выходы.

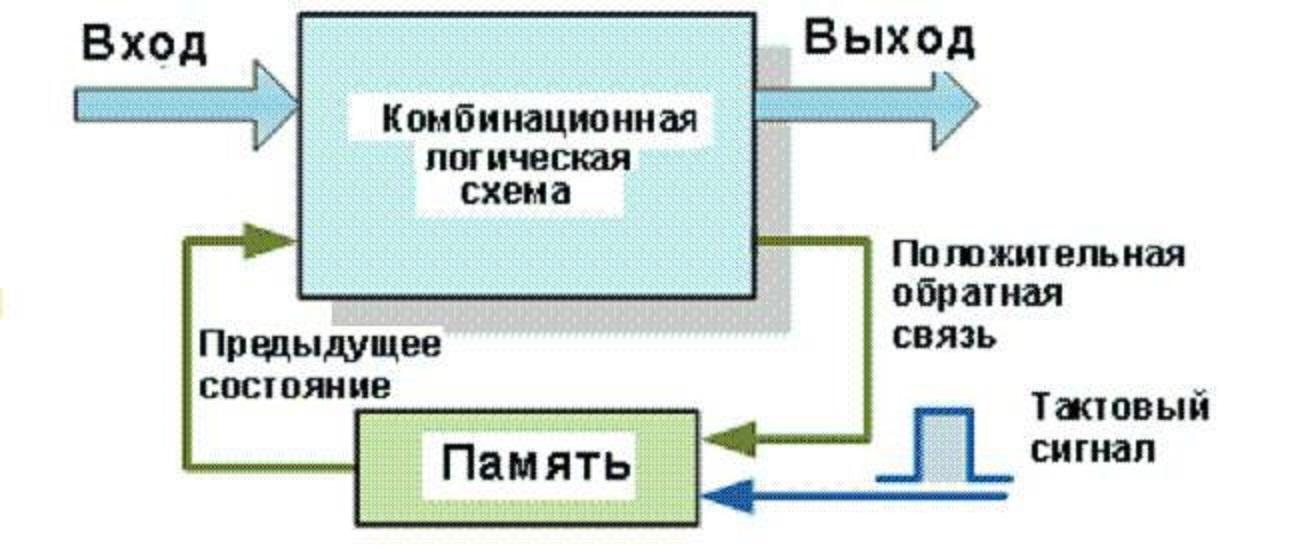

Место триггеров в цифровой схемотехнике

Сам рс триггер, как один из структурных элементов в схемотехнике, не содержит в своём составе какого-то отдельного блока или устройства памяти. Он является простейшей логической ячейкой, которая запоминает своё предыдущее и настоящее состояния на входах и выходах. Память является результатом алгоритма работы переключателя. Выходы устройства находятся в состоянии либо логического нуля, либо единицы. При их изменении схема «защёлкивает» это положение и запоминает до тех пор, пока устройство управления вводом, выполненное из логических элементов, не даст команду об изменении состояния.

Классификация

Прежде, чем рассматривать работу триггеров, необходимо разобраться в обозначениях входов и выходов подобных устройств.

Входа (порты) у триггера бывают:

- R (reset) – устанавливает положение 0, раздельный порт;

- S (set) – устанавливает положение 1, раздельный порт;

- J – порт универсальных защёлок, устанавливает статус 1;

- K – порт универсальных защёлок, устанавливает статус 0;

- T – счётный порт, меняет положение защёлки.

У защёлки в наличии два выходных порта:

- Q – прямой;

- Q¯ – инверсный.

При единице на прямом (Q = 0) «защёлка» находится в состоянии «1». В случае низкого потенциала на выходе (Q = 1) статус защёлки – «0».

У инверсного выхода все наоборот. При нуле у выхода Q¯ переключатель находится в состоянии единицы. Инверсия положения нужна для внедрения различных схематических решений.

Внимание! Типы портов определяют названия электронных переключателей, так, имея порта R и S, он носит имя RS-триггер.

Последовательностное логическое устройство (ПЛУ), которым является «защёлка», – это своеобразный блок для постройки различных комбинаций в схемах логических цепей. Бистабильное состояние RS-защёлки помогает компоновать такие логические схемы, как счётчики, регистры хранения, устройства памяти или регистры сдвига. Независимо от метода устройства логических связей, основные виды электронных переключателей можно разделить по способу ввода данных:

- синхронный тип;

- асинхронный тип;

- комбинированный.

Всё зависит от того, как посылается команда управления на изменение состояния «защёлки».

Синхронные устройства

Для того чтобы rs триггер не менял своего положения от сочетания задержанных командных импульсов на его портах, применяют синхронизирующую команду. Это тактовый импульс, который подаётся на синхронизирующий порт. Сменившиеся сигналы на входах такой «защёлки» не смогут изменить состояния на выходе, пока не придёт тактовый (синхронизирующий) импульс. Эти импульсы вырабатывают тактовые генераторы. Длина тактовых сигналов намного меньше их периода. Импульсы определяют частоту замены информации, привязав её к дискретным временным периодам – tl, t2,…,tn-1,tn, tn+l. Это позволяет синхронизировать процессы работы отдельных узлов оборудования в едином ритме.

Действие схемы следующее:

- если на порту С присутствует ноль, статус триггера не меняется, поскольку информация с портов S и R не передаётся на защёлку;

- если на порту С появляется логическая единица, то переключатель принимает команды с S и R входов и меняет своё положение.

У таких схем повышенная помехоустойчивость, что выгодно отличает их от асинхронных устройств, последние могут перевернуться не только от сигнала, но и от помехи. Синхронная структура применяется в технике, связанной с преобразованием или обработкой цифровых данных.

Асинхронные модели

Устройство, меняющее своё состояние немедленно при изменении команды на логических портах, называют асинхронным триггером. Он имеет в своём составе только порты: R (сброс) и S (установка). Ограничения для пользования подобными схемами связано с соперничеством между сигналами, которые при попадании на разные входы RS-триггера движутся разными путями, как бы состязаясь между собой. При этом возникают временные задержки и сдвиги, вызванные разными причинами: изменения температуры, долгий срок службы и прочее. Такая «гонка» вызывает частые ошибочные переворачивания ячейки.

Тактовая синхронизация в данном случае не эффективна, потому асинхронные ячейки применяются в качестве асинхронных счётчиков, различных ключей, делителей частоты и им подобных схемных решений.

Комбинированные схемы

Модуль, состоящий из комбинации нескольких ячеек, называется комбинированным триггером. Возможны комбинации от двух и более функциональных ячеек.

Таблица комбинаций двух типов ячеек памяти

| Тип устройства | RS | R | S | E | JK | T | D | DV |

|---|---|---|---|---|---|---|---|---|

| RS | Х | Х | Х | Х | Х | Х | Х | |

| R | Х | Х | Х | Х | Х | Х | ||

| S | Х | Х | Х | Х | Х | |||

| E | Х | Х | Х | Х | ||||

| JK | Х | Х | Х | |||||

| T | Х | Х | ||||||

| D | Х | |||||||

| DV |

Типы триггеровЗдесь Х – объединение двух типов возможно.

Подразделение этих устройств по типам можно рассмотреть по таблицам переходов состояния.

Выделяются следующие типы ячеек памяти состояния:

- rs-защёлка – асинхронная и синхронная;

- jk-защёлка;

- d-защёлка;

- t-защёлка.

Последний элемент списка – устройство составное, выполняется из синхронной rs-ячейки памяти.

RS-триггеры

Рассматривают два вида подобных ячеек: асинхронная и синхронная защёлка. При подробном изучении видна значительная разница в работе и сфере применения.

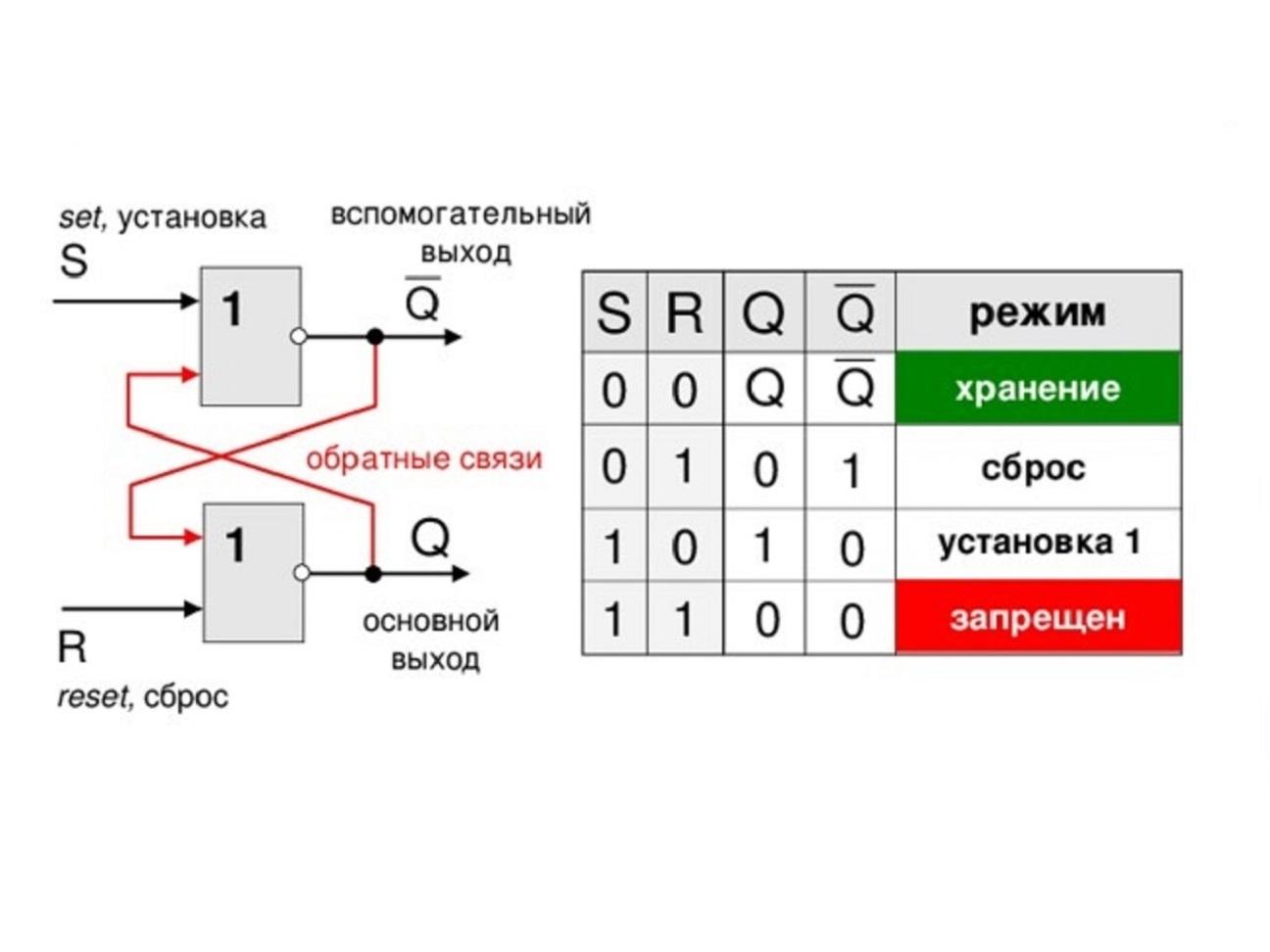

RS-триггер асинхронный

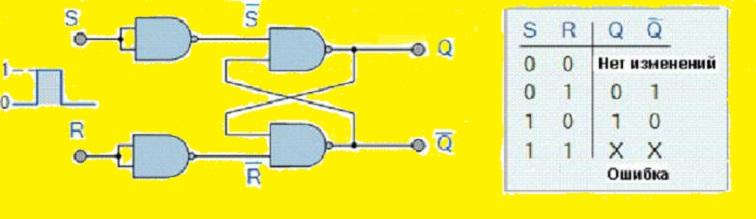

Самый простой вид защёлки, редко применяется как самостоятельное устройство, является ячейкой для построения более сложных блоков. Построены асинхронные соты на элементах:

- 2 ИЛИ – НЕ, триггерная сота с прямыми портами;

- 2 И-НЕ, триггерная сота с инверсными портами.

Фиксированные положения триггеру обеспечивают обратные связи. Это подключение выхода одного к любому входному порту другого логического элемента.

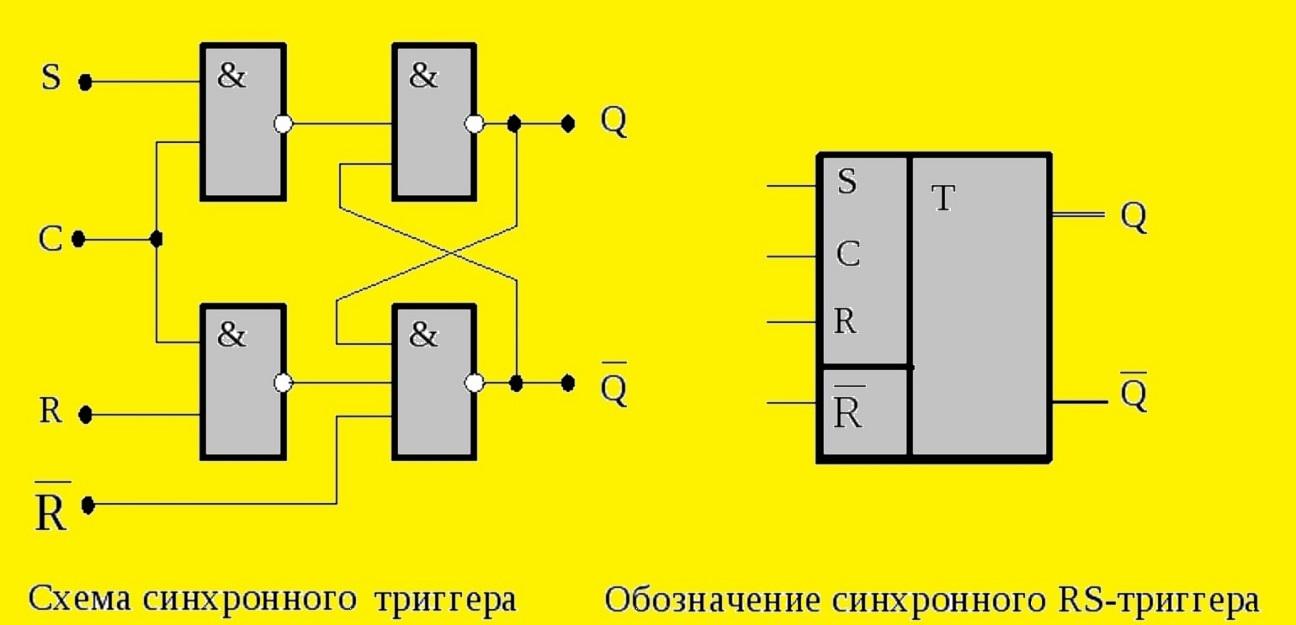

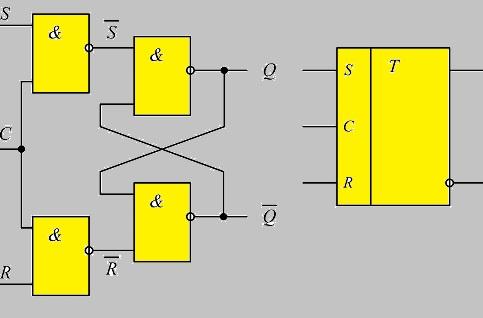

RS-триггер синхронный

Основа регистров, делителей частоты и различных счётчиков – триггерная сота памяти. В подобных устройствах зафиксированную раньше информацию нужно передать на выход и записать в следующую ячейку по сигналу тактового импульса. Импульс подаётся на С-порт (статический или динамический).

Состоящие из пары синхронных rs-триггеров и инвертора двухступенчатые RS-триггеры управляются полным (задействованы и фронт, и срез) динамическим тактовым импульсом. Такие ячейки памяти называются master-slave (мастер-помощник).

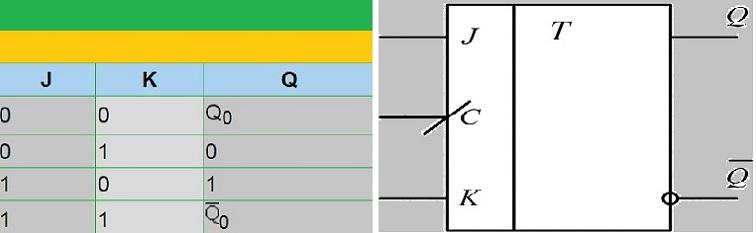

JK-триггер

Отличительной чертой этого типа «защёлки» является отсутствие запрещённого сочетания сигналов на портах. При J = K = 1 положение защёлки переворачивается на обратное, по сравнению к текущим Q0.

JK-переключатель отличается от RS-ячейки памяти только одним: если на J и K подаётся «1», то он меняет своё пребывание на противоположное положение. Происходит инверсия, причём у этой ячейки памяти отсутствуют запрещённые состояния главных портов.

Что такое RS триггер

Это сота памяти, способная находиться в одном из стабильных положений: «0» или «1». Переворачиваться, т.е. менять их, она может под воздействием тактовых сигнальных импульсов. Ни записать, ни стереть хранимый бит элементарный элемент, собранный на двух инверторах, не может. Принцип работы rs триггеров, выполненных на двух компонентах 2И-НЕ, позволяет это сделать.

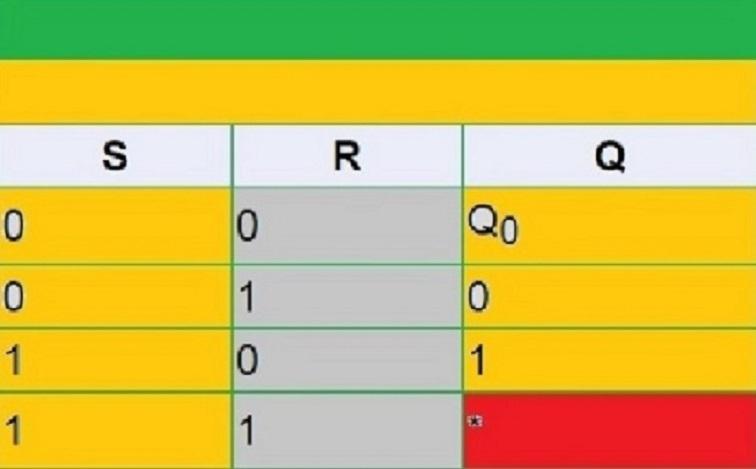

Таблица истинности

Таблица переходов состояний (таблица истинности) поясняет работу RS-триггера на элементах «И-НЕ». На ней Q 0 – текущий статус ячейки до попадания активного сигнала на порт. Когда логическая единица отсутствует на входах R и S, «защёлка» сохраняет положение Q 0. Активный импульс R = 1 перекидывает защёлку в положение 0, импульс S = 1 – в положение 1. Звездочка в таблице указывает на положение при запрещенном сочетании приходящих сигналов.

Такой тип имеет раздельное назначение логических состояний нуля и единицы по информационным портам.

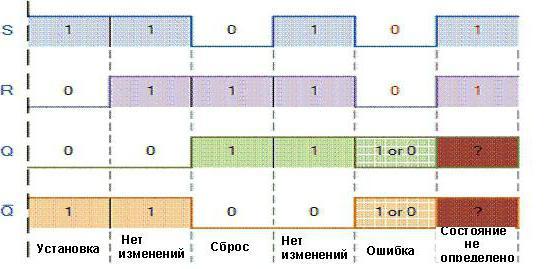

Временные диаграммы

Кроме таблиц истинности, помогает разобраться в работе ячейки битовой памяти временная диаграмма. При этом на графике при изучении импульсов рассматривают следующие параметры:

- длительность импульса – временной интервал от фронта до спада;

- период – интервал от фронта предыдущего импульса до фронта последующего;

- скважность – отношение периода импульса к его длительности.

Диаграмма графически отображает сигнальные импульсы на входах и выходах в одних и тех же временных точках.

Классификация последовательных схем

Последовательные схемы допускается классифицировать по следующим показателям:

- одноступенчатые защёлки, в которых содержатся элемент памяти и устройство управления, их маркируют буквой Т;

- двухступенчатые ячейки: статического и динамического управления, используются для защиты от гонок сигналов, обозначаются буквами ТТ;

- переключатели, имеющие сложную логику: одно,- и двухступенчатые соты.

Одноступенчатые ячейки применяются в качестве первых ступеней в переключателях ТТ с динамической схемой управления, имеют такое же управление. При самостоятельном использовании управление в большинстве своём статическое.

Двухступенчатые устройства имеют как статическое, так и динамическое управление.

Состояние «Установлен»

RS-переключатель в этом состоянии имеет установленную цепь с Q, равным нулю, и Q¯, равным единице, и независим от управляемого сигнала. При этом на R присутствует ноль, на S – логическая единица.

Состояние «Сброшен»

Это тоже неизменная ситуация. Для её организации необходимо выставить исходные условия. На R подаётся «1», на S – «0». При этом выход Q должен иметь «1», Q¯ – значение «0». Обратные связи обеспечивают и фиксируют независимое от последующих значений на входах значение.

Диаграмма переключения RS-триггера

Состояния переключения, установки и сброса можно просмотреть на временной диаграмме. На ней отмечено, что переключатель переходит в положение установки при появлении нуля на его S-входе и единице на входе R, фиксированный сброс при подаче нуля на порт R и единицы на S.

Модификация схемы триггера

Чтобы смена состояний происходила на подъёме уровня сигнала у rs-триггера, необходимо на его выходах иметь:

- при установке – Q = 1, а Q¯ = 0;

- при сбросе – Q = 0, а Q¯ = 1.

Чтобы это организовать, поступающие сигналы защёлки инвертируют. В результате этого изменение состояния выполняется при поступлении положительных сигналов. При модификации добавляются в качестве инверторов 2 элемента И-НЕ.

Как синхронизировать работу триггера

Подключение двухпортового элемента «И» в последовательную цепь схемы триггера с каждым из входов позволит менять его статус, независимо от состояний на R,- или S-входах. Новый порт С получится при объединении двух портов ячеек «И». В результате доработки статус на выходах Q и Q¯ будет меняться только тогда, когда на С будет приходить высокий потенциал. Предусмотрено подключение генераторов тактовых импульсов на этот новый вход.

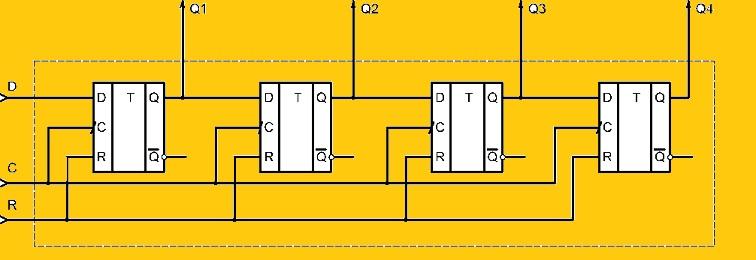

Регистры на триггерах

Так как один переключатель является однобитовой ячейкой памяти, то, чтобы сохранить несколько бит, нужно увеличить количество единичных хранилищ. Цепочка из таких ячеек носит названия регистра. Регистр позволяет временно хранить цифровые данные двоичных разрядов. Количество разрядов зависит от количества однобитовых ячеек.

Использование элементарных электронных цифровых устройств – триггеров, позволяет составлять сложные схемы управления логическими устройствами. Одна элементарная защёлка памяти своим бистабильным состоянием помогает осуществлять самые сложные схемные решения.